![]()

測試環境 Windows 10 + Excel 2016

在 Excel 的 VBA 可以透過 Sheets.Add 方法來新增 worksheet(工作表), 有辦法當無該 worksheet 時才新增該 worksheet 嗎?

參考文章 https://stackoverflow.com/questions/17218999/if-sheet-doesnt-exist-create-it-vba-excel

寫成 Add_Sheet 函數.

Function Add_Sheet(sheet_name As String)

Dim i, sheet_exists As Integer

sheet_exists = 0

For i = 1 To Sheets.Count

If Sheets(i).Visible = -1 Then

If Sheets(i).Name = sheet_name Then

sheet_exists = 1

End If

End If

Next

If sheet_exists = 0 Then

Sheets.Add(After:=Sheets(Sheets.Count)).Name = sheet_name

End If

End Function

使用時直接呼叫即可.

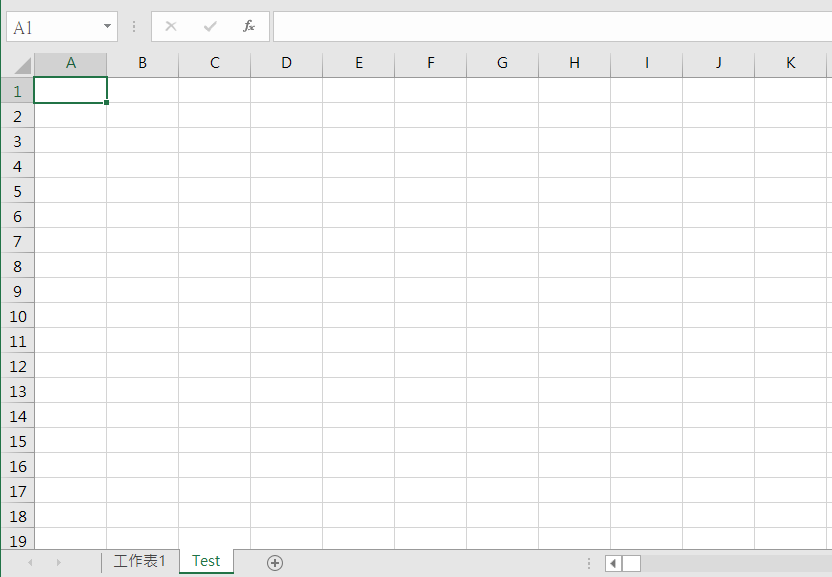

Sub Test1()

Add_Sheet ("Test")

End Sub

沒有解決問題,試試搜尋本站其他內容

One thought on “Excel VBA – Sheets.Add 方法”